IBM的研究人员及其合作伙伴共同开发出基于堆叠硅晶奈米片(nanosheet)的新电晶体架构,据称这种奈米片电晶体可望用于5nm节点製造FinFET元件。

在本週于日本京都举行的「超大型积体电路技术暨电路会议」(2017 Symposia on VLSI Technology and Circuits)上,IBM及其研究联盟合作伙伴——包括GlobalFoundries、三星(Samsung)以及设备製造商,共同发表这个在奈米片累积十年研究的新架构。根据研究人员们表示,该新架构的功耗比FinFET更低许多。

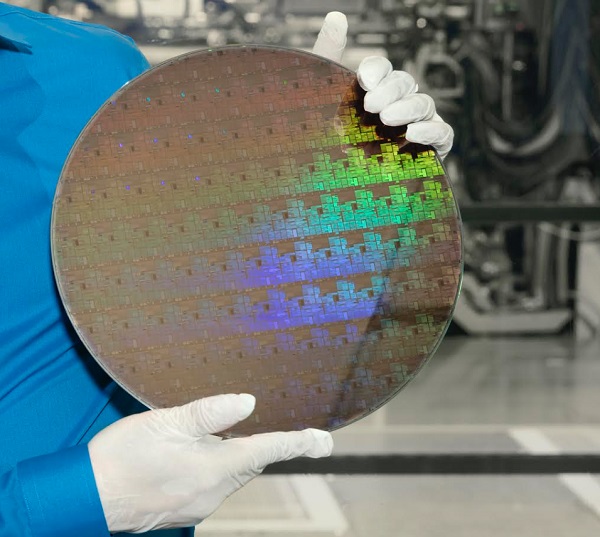

IBM/GlobalFoundries/三星的研究人员共同开发革命性的5nm奈米片电晶体,採用闸极环绕式(GAA)架构,据称可望为智慧型手机带来2-3天的电池使用寿命(来源:IBM)

研究人员们表示,这项突破可望让以电池供电的装置(智慧型手机与其他行动装置)在一次充电后持续2-3天的使用寿命,以及提高人工智慧(AI)、虚拟实境(VR)以及甚至超级电脑的效能。

在开发具有200亿闸电晶体的7nm测试晶片约两年后,研究人员们表示至今已为实现具有300亿闸电晶体的微型晶片铺好路了。据称这款微型晶片的尺寸只有指甲般的大小,并搭载四相GAA奈米线。测试结果显示,在与7nm FinFET的相同功率下,效能提升了40%,或较当今先进的10nm电晶体更省电75%。

IBM研究科学家Nicolas Loubet手持採用5nm硅晶奈米片电晶体的晶圆(来源:IBM)

IBM指出,新的5nm技术在效能上的突破,将有助于提升其于认知运算的开发,以及朝向更高吞吐量的云端运算与深度学习,以及为所有的行动物联网(IoT)装置降低功耗,并延长其电池的使用寿。

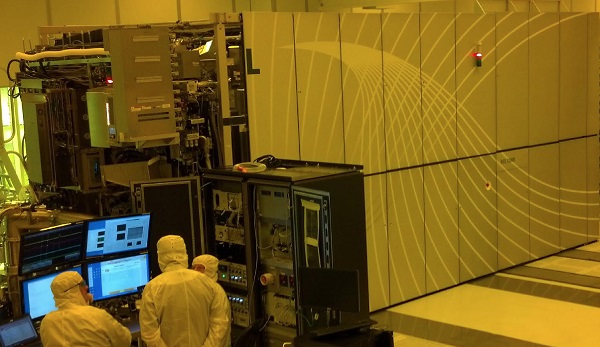

美国纽约州立大学理工学院(SUNY Polytechnic Institute)奈米科学与工程学院的奈米技术中心(NanoTech Complex)正準备5nm硅晶奈米片电晶体的测试晶圆,以测试製造硅晶奈米片的技术製程(来源:SUNY)

为了达到这一技术突破,该研究联盟必须克服阻碍极紫外光(EUV)微影的问题;目前,EUV 微影技术已经出现在生产7nm FinFET的开发蓝图上了。研究联盟发现,EUV除了具有波长更短的优势,还找到了以晶片设计和製程阶段中持续调整其奈米片宽度的方法。根据研究人员表示,FinFET由于受限于其鳍片的高度而无法微调其性能以及折衷功率,从而使其无法为实现更高性能而增加电流。

研究人员们在位于纽约州阿尔巴尼的科学与工程学院奈米技术中心监看业界最先进製程採用EUV微影工具在的操作状况;该製程技术的目标在于打造可实现5nm晶片的硅晶奈米片电晶体(来源:SUNY)

IBM认为,就单储存单元的DRAM、化学放大光阻剂、铜互连、绝缘上覆硅(SOI)、应变材料、多核心处理器、浸润式微影、高K电介质、嵌入式DRAM、3D晶片堆叠和气隙绝缘层而言,其奈米片架构的重要性并不亚于该先进製程技术的突破。除了在单

Globalfoundries技术长兼全球研发负责人Gary Patton认为,这项宣告具有「开创性」的意义,并展现Globalfoundries正积极追求5nm节点以及更先进的下一代技术製程。

编译:Susan Hong

(参考原文:IBM Claims 5nm Nanosheet Breakthrough,by R. Colin Johnson)

加QQ群|

加QQ群|

二维码|

二维码|